文|芯世相

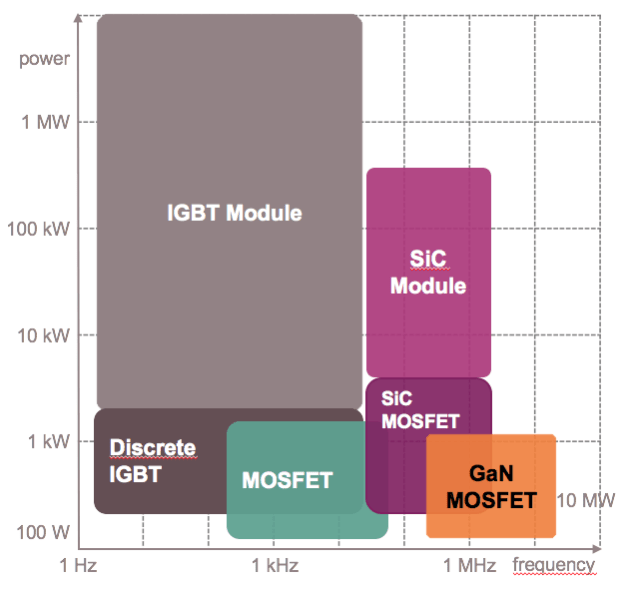

功率半导体供应商在持续开发和交付基于传统硅技术的设备,但硅已接近它的性能极限,并面临来自 GaN 和 SiC 等技术的日益激烈的竞争。

作为回应,业界正在寻找扩展传统的硅基功率器件的方法。至少在短期内,芯片制造商正在努力提高性能并延长技术的应用时间。

功率半导体是用于从低压到高压多种应用场景的专用晶体管,例如汽车、工业、电源、太阳能和火车。这些晶体管像设备中的开关一样工作,允许电流在“开”状态下流动并在“关”状态下停止。它们提高了设备的运作效率,并最大限度地减少了设备系统中的能量损失。

多年来,功率半导体市场一直由硅基器件主导,即功率 MOSFET、超结功率 MOSFET 和绝缘栅双极晶体管(IGBT)。这些硅基器件于上世纪70年代首次实现商业化,如今几乎在每个系统中都能找到。这些产品在技术上比较成熟且价格低廉,但它们也有一些缺点,并且在某些情况下达到了理论性能极限。

这就是为什么许多供应商也在开发和交付基于两种宽带隙半导体——氮化镓(GaN)和碳化硅(SiC)的新型功率器件。在一段时间里,市场上GaN和硅基功率器件在不同领域与硅基IGBT和硅基MOSFET竞争。虽然GaN 和 SiC 器件效率更高,但它们也更昂贵。

总的来说,这些不同类型的功率半导体为客户提供了选择,但它们也增加了一定程度的混乱。事实证明,没有一种功率器件可以满足系统中的所有要求。这就是客户需要一系列具有不同额定电压和价位的选项的原因。

GaN 和 SiC 器件在近期备受关注。它们是新一代半导体,并提供了各种令人印象深刻的属性。但成熟的硅基器件也很重要,它们不仅不会很快消失,而且会继续发展,尽管速度比前几年慢。

全球最大功率半导体供应商英飞凌的应用管理总监 Bob Yee 表示:“今天我们看到,即使宽带隙技术出现,硅仍将是功率MOSFET的主导形式,约占市场的60%。”

他还表示:“宽带隙将填补并占据硅的空间,从而增加更多价值,并将在硅无法实现的地方实现新的应用。也就是说,宽带隙是对硅的补充,但在可预见的未来,硅仍将是主力。”

换句话说,所有技术都有一席之地。总而言之,基于硅的功率半导体器件,包括 IGBT 和 MOSFET在内,仍占整个市场份额的 80% 左右。如今在硅的竞技场上已经发生了几项大事,包括:

供应商正在推出新系列的硅基功率MOSFET、超级结器件和IGBT。在研发方面,业界正在推进基于硅的 MOSFET 和 IGBT。Lam Research 和其他公司开发了用于功率半导体的新设备。

功率半导体用于电力电子领域,使用固态设备,用电力电子控制、转换各种系统中的电力,例如汽车、电机驱动器、电源、太阳能和风力涡轮机。

这些器件不同于传统的金属氧化物半导体场效应晶体管(MOSFET)。当今的数字 CMOS FET 由构建在硅顶部的源极、栅极和漏极组成。在操作中,向栅极施加电压,使电流从源极流向漏极。

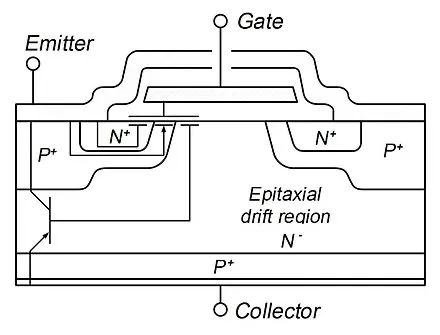

相比之下,IGBT 和大多数功率 MOSFET 是垂直器件,源极和栅极位于器件顶部,漏极位于底部。在操作中,向栅极施加电压并且电子沿垂直方向移动,垂直方向支持更高的电流和电压。

同样地,它们还有其他差异。在传统的 MOSFET 中,芯片制造商在其每一代都会缩小晶体管的特征尺寸,从而使芯片具有更高的晶体管密度。在功率器件中,供应商也在缩小晶体管,但还没有达到数字 CMOS 的程度。

Lam Research战略营销高级总监 Michelle Bourke 表示:“如果要探讨 MOSFET 和 IGBT,它们在规模和效率方面其实正在经历自己的发展轨迹。” “有些人可能会说,与 CMOS 相比,它们的功能很强大。但是,为达到该设备性能所需的垂直度和配置文件控制,这与我们在公司中遇到的CMOS 问题一样具有挑战性。因此,虽然从设备的角度来看,这些功能仍然很强大,但从开发的角度来看,这是我们完成的最具挑战性的过程之一。我们正在实现这一点。”

通常来说,对于功率半导体最重要的考虑因素是其他参数,例如电压 (V)、Rds(on)和栅极电荷。每个功率半导体器件都有一个额定电压(V)。“VDSS 中的 'V' 是最大允许工作电压,或漏源电压规格。”EPC 首席执行官 Alex Lidow 解释道。

On电阻或Rds(On)是源极和漏极之间的电阻值,栅极电荷是开启设备的电荷量,Rds(on)x A(area) 很重要。“半导体业务的成本优化一直与芯片缩小相关,此规则也适用于功率器件。Ron x A 是一个关键品质因数,它描述了提供功率器件的特定器件性能所需的硅面积。通常,当我们开发新的电源技术时,我们通过降低新技术的 Ron x A 来获得的成本优势超过了通常更复杂的生产过程的额外成本。这些成本效益可以移交给客户,这是降低成本路线图的核心。”英飞凌的 Yee 说。

为了适应不同的应用,目前有多种功率半导体选项可供选择。在硅方面,可选择的包括功率 MOSFET、超结功率 MOSFET 和 IGBT:

功率 MOSFET 被认为是最便宜和最受欢迎的器件,用于适配器、电源和其他产品,用于 25 V-500 V的应用。

超结功率 MOSFET 是增强型 MOSFET,用于 500 V-900 V系统。同时,领先的中端功率半导体器件是用于 1,200 V-6.6 kV应用的 IGBT。

硅基功率器件在各个领域与 GaN 和 SiC 竞争。GaN 和 SiC 都具有一些令人印象深刻的特性。SiC 提供 10 倍的击穿电场强度和 3 倍的硅带隙,GaN 则超过了这些数字。

“宽带隙半导体具有关键优势,但它们将与基于硅的技术并行存在。”Lam Research 战略营销董事总经理 David Haynes 说。“基于硅的技术将持续很长时间,它们非常成熟,而在基于硅的功率器件方面,也在进行着大量的研究和技术开发。”

1969 年,日立公司向我们介绍了世界上第一个功率 MOSFET。随着时间的推移,越来越多的公司加入到功率 MOSFET 市场,功率 MOSFET 同时也发展成一项大产业。

根据 Yole Développement 的数据,2020 年,整个功率 MOSFET 市场的业务规模为 75 亿美元。Yole 称,该市场正以每年 3.8% 的平稳速度增长。其中,英飞凌是最大的功率 MOSFET 供应商,其次是许多其他供应商。

功率 MOSFET 用于 25 V- 500 V的应用,几乎在每个应用系统中都可以找到。通常来说,它们由 200 mm和 300 mm的晶圆厂制造。

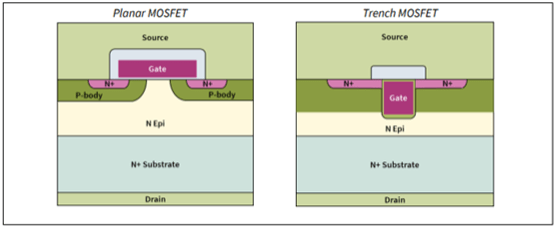

多年来,功率 MOSFET 得到了改进。根据 B. Jayant Baliga 在其《功率半导体器件基础》一书中的说法,在上世纪70年代,第一批器件是基于平面栅极结构。Baliga 是 IGBT 的发明者,一名来自北卡罗来纳州立大学的教授。

这个功率 MOSFET 的顶部有一个源极和栅极,底部有一个漏极,它有时也被称为平面功率 MOSFET。

根据 Baliga 的说法,在上世纪90年代,供应商转向基于沟槽的栅极结构,它仍然是一个垂直设备,但基于沟槽的功率 MOSFET 不具有水平栅极结构,而是在结构中具有垂直栅极。这种基于沟槽的功率 MOSFET 能够以更小的芯片尺寸实现更高的密度。

随着时间的推移,供应商根据应用同时使用了平面和垂直栅极。他们还利用了设计和制造领域的各种创新,以便继续改进产品。

例如,最近英飞凌推出了最新的功率 MOSFET 系列 — OptiMOS 6。这些器件的 Rds(on) 比上一代产品低 18%。

其他供应商也正在出货新的功率 MOSFET。此外,它们正在研究更新的技术,例如,Applied Novel Devices (AND) 正在开发具有类 GaN 性能的功率 MOSFET,SkyWater 是 AND 的代工合作伙伴。

“随着硅的每一代迭代,我们减小了沟槽的单元间距。”英飞凌的 Yee 说。“这就是说我们正在降低 Rds x A ,这会导致品质因数较低,从而使应用程序更快地切换。Rds x A 的降低使供应商能够降低 MOSFET 的总体成本,同时提高性能。”

尽管如此,推进功率 MOSFET 仍存在挑战。“在保持器件热特性的同时,进一步降低性能因数[Rds(on)x栅极电荷],始终是一个挑战。”Yee说。

虽然供应商正在寻找通过新设备获得更高性能的方法,但他们也在调整晶圆厂的制造工艺。一般来说,功率MOSFET工艺已经成熟,但也存在一些问题。

在晶圆厂中,供应商对平面栅极和沟槽栅极功率 MOSFET 使用了许多相同的工艺步骤,但存在关键差异。这两种技术的第一步都是在衬底上沉积一层薄的 N+ 外延层,该层称为漂移区。

在器件上沉积掩模层,掩模层覆盖设备顶部,但设备两侧的边缘除外。根据Baliga 的说法,边缘植入了P型掺杂剂。

epi堆叠的厚度是关键。外延层的厚度与最终器件的阻断电压直接相关。根据AOS万国半导体的说法:“例如,更厚、更轻掺杂的epi(堆栈)支持更高的击穿电压,但导通电阻增加。”然后,在器件上形成沟槽。沟槽的尺寸由原始设计确定。在某些情况下,沟槽尺寸可能为1.5μm或更小。

为了形成沟槽,还要在器件上沉积另一个掩模层。这次,中间部分被暴露,其中注入了N型掺杂剂。

为了形成沟槽,还要在表面上沉积氧化物,沟槽被图案化,然后被蚀刻。沟槽填充有栅极材料,最后形成源极和漏极。

所有这些步骤都很重要,尤其是蚀刻过程。使用蚀刻工具,功率MOSFET中的沟槽通常使用SF6/O2等离子体工艺进行蚀刻。

KLA公司SPTS产品管理副总裁戴夫·托马斯(Dave Thomas)说:“这是大多数晶圆厂使用的方法。侧壁平滑度和底部圆整度是关键。SF6/O2方法让你对硬口罩有合理的选择性,并允许你拥有相对较高的深度和纵横比。SF6/O2连续法的一个限制是你将要达到的绝对深度,你只能达到一个不能再保持侧壁质量的特定点。这是由于防止硅蚀刻移动和通过氧化保护蚀刻侧壁之间的微妙平衡(即平衡SF2和O2的比率)。因此,对于更深层次的结构,Bosch工艺(一种刻蚀工艺)更合适。然而,关键点是通过最小化Bosch蚀刻扇形孔,使侧壁光滑。”

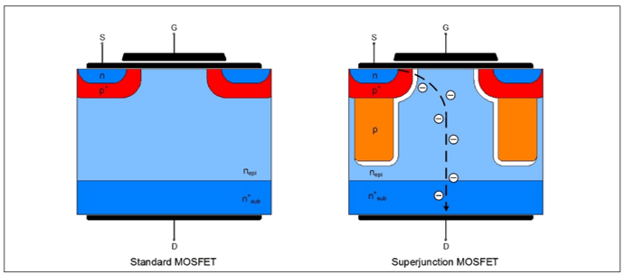

功率 MOSFET 也有一些局限性,因此在几年前,业界开发了超结功率MOSFET。超结器件仍以硅为基础,用于 500 V-900 V的应用。

这些器件类似于功率 MOSFET。最大的区别在于,超结功率MOSFET在结构内由垂直的高纵横比P/N柱组成,具有一些优势。

“超结功率 MOSFET 可在更小的空间内实现更大的功率。其次,它为关键任务应用提供了可靠性。”英飞凌的 Yee 说。“每一代,我们都在不断改进设备参数,例如Rds(on)、降低栅极电荷以及Eoss(存储在输出电容中的能量)。”

事实上,这些设备还在不断发展。例如,英飞凌的超结功率 MOSFET 系列,称为 CoolMOS,目前已进入第七代,新一代正在酝酿之中。此外,Alpha 和 Omega、Magnachip、Rohm、Toshiba 等公司正在出货新的超结功率 MOSFET。

然而,一般来说,超结技术正在达到自己的极限。“经过 20 年的发展,超级结功率 MOSFET 在 Rds(on)x A 方面存在物理限制,但仍然会有几代超级结的改进。宽带隙的出现无疑将在未来几年接替这种对性能提升的追求。重申一下,在可预见的未来,超结 MOSFET 将与宽带隙技术共存。”Yee 说。

供应商仍在寻找扩展超结器件的方法,但也存在一些挑战。按照传统,为了在晶圆厂中制造超级结 MOSFET,供应商会在基板上堆叠多个外延层。在每一层都有一个掩膜和注入步骤,这又在器件中形成 P 型柱,然后形成源极、漏极和栅极。

这种方法有效,但产生的 N 型和 P 型结构更大,这反过来又会影响芯片尺寸。

因此,在 2008 年,DENSO公司开发了一种不同的方法,并在市场上获得了成功。在该流程中,N型外延层沉积在衬底上,接下来,使用蚀刻工具,在外延层中以高纵横比形成垂直沟槽。

接着,根据DENSO的说法,P 型材料被沉积在沟槽中,形成 P 型柱。这导致设备具有交替的 P/N 列。形成栅极、源极和漏极。

“(这种方法)改善了击穿电压和特定导通电阻之间的权衡关系。”DENSO 的 Jun Sakakibara 在 2008 年的原始论文中说。

这里存在一些制造挑战,即在结构内制作高纵横比(HAR)沟槽。

“制造超级结 MOSFET 有不同的机制,其中许多涉及高纵横比沟槽蚀刻。这些纵横比可以是 40:1 到 50:1,并且越来越多的纵横比可以高达 80:1 或 100:1。这是硅蚀刻的一系列新挑战。与 IGBT 或传统 MOSFET 沟槽不同,这些极深的 HAR 超级结 MOSFET 沟槽无法使用 CMOS 制造中使用的稳态蚀刻工艺类型进行蚀刻。”LAM 的 Haynes 说。

换句话说,它需要一种不同的解决方案,即反应离子蚀刻(RIE)工具。“它们需要使用深度反应离子蚀刻工艺进行蚀刻,该工艺在蚀刻和侧壁钝化沉积之间切换,以实现深度蚀刻能力。”Haynes 说。

在 RIE 中,第一步是蚀刻掉结构的一部分,然后将其钝化。然后重复该过程,直到蚀刻完成。这称为Bosch工艺。

多年来,一些供应商已经为这些应用程序开发了 RIE 工具。例如,LAM 最近推出了一种新的 RIE 工具设计来应对 HAR 挑战。LAM 的新工具 Syndion GP 为所有功率器件和其他产品提供深度硅蚀刻能力,它支持 200mm 和 300mm 晶圆。

“我们制造功率器件的客户可能在同一条生产线上制造 IGBT、MOSFET 和 SJ-MOSFET,因此在开发 Syndion GP 工具时,我们希望在同一工具中同时提供稳定状态和深度 RIE 工艺的功能。”Haynes 说。

与此同时,IGBT 仍然是领先的中档功率器件。IGBT 作为一种垂直器件,结合了 MOSFET 的开关速度和双极器件的导电性。

据 Yole 称,IGBT 在 2020 年的业务价值为 54 亿美元,预计每年增长 7.5%。富士、英飞凌、Littlefuse、三菱、安森美、东芝等都在这里展开竞争。

这些器件用于汽车、消费和工业应用。在一些电池电动汽车(BEV)中,IGBT 用于牵引逆变器,它为电机提供牵引力以驱动车辆。

特斯拉在其 Model 3 BEV 中使用具有竞争力的 SiC 功率器件作为牵引逆变器。展望未来,BEV 制造商可能会同时将 IGBT 和 SiC 器件用于功率逆变器。

多年来,IGBT 得到了改进。去年,英飞凌推出了基于其第七代 IGBT 系列的新模块。基于微图案沟槽技术,这些器件的开关损耗比之前的产品低 24%。

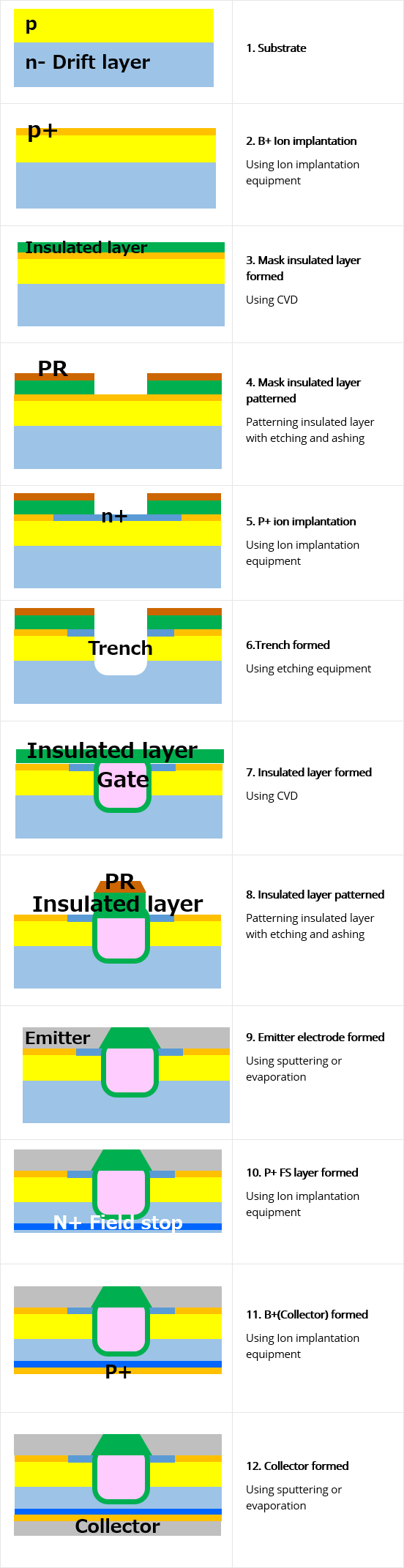

与功率 MOSFET 一样,IGBT 由平面或沟槽栅极结构组成。在更先进的基于沟槽的 IGBT 中,该工艺首先在衬底上沉积四个交替外延层(PNPN)。

表面经过 P 型注入步骤,之后,为了形成沟槽,对该结构进行构图和蚀刻,然后用栅极材料填充沟槽结构。最后,采用沉积技术,在顶部形成发射极,在底部形成集电极。

IGBT 已经存在了几十年,但最新的器件面临着一些制造挑战。“如果你采用 IGBT,就会通过制造越来越薄的晶圆来降低导通电阻,同时提高功率密度。当你增加功率密度时,你会增加沟槽的密度,可以从过去是方形或六边形的单元阵列,变成非常密集的沟槽。”LAM 的 Haynes 说。

沟槽的纵横比也增加了。“现在使用的特征尺寸可能是 7 到 10 微米深,随着图案密度的接近,纵横比正在增加,但在 RIE 蚀刻工艺中,需要良好的轮廓控制。它们在非常高的电压下工作,沟槽的任何畸形或沟槽轮廓的任何不均匀都可能导致故障。”Haynes 说。

还有其他挑战。“在晶圆的正面,你正在对栅极和源极 (MOSFET)/发射极 (IGBT) 连接进行接触金属化,由于功率器件涉及高电流,因此金属必须比常规半导体器件厚。金属,通常是通过 PVD 沉积的铝合金(通常是 AlSi 或 AlSiCu),可以是 3μm 或高达 10μm 厚的任何东西。接触往往是基于长沟槽的结构,但也可以存在圆形或开槽接触。尺寸通常为 1-2μm 宽,具有低纵横比。但随着人们使用更先进的设备,他们可能会将接触尺寸缩小到 0.5μm 宽度,纵横比为 2:1,将铝放入低纵横比触点相对容易。”KLA 公司 SPTS 的 PVD 产品管理高级总监 Chris Jones 说。

尽管如此,供应商仍在继续开发基于硅的 IGBT。在研发方面,供应商和大学正在研究新奇的设备。

例如,在 2020 年 IEDM 会议上,多家实体发表了一篇关于 3.3kV 背栅 IGBT(BC-IGBT)的论文,东京大学、三菱、东芝等为这项工作做出了贡献。

BC-IGBT由结构顶部和底部的栅极组成。“IGBT的一个主要缺点是由于其基带中电荷载流子的积累,其开关频率相对较低,通过使用背面MOS栅极加速电子漏极和空穴注入阻塞,关断损耗降低了60%以上。”东京大学的研究人员Takuya Saraya说。

开发背栅IGBT的一种方法是制造两个单独的器件,然后将它们连接在一起,但这增加了成本。

在BC-IGBT技术中,研究人员开发了一种传统的IGBT。之后,他们在设备底部实施了传统的沟槽工艺,两扇门都对齐了。

-PG电子(中国)官方网站